1. Inleiding

Klokoscillatoren genereren zeer stabiele kloksignalen die nodig zijn in vrijwel alle elektronische systemen – van eenvoudige microcontrollercircuits tot snelle datatransmissiesystemen.

Het uitgangssignaal van een oscillator moet compatibel zijn met de daaropvolgende logicafamilie of interface. In de loop der decennia zijn verschillende uitgangsstandaarden ontwikkeld, elk afgestemd op de eisen van hun tijd en toepassing.

Dit document biedt een uitgebreid overzicht van de zeven meest voorkomende uitgangssignaaltypen in warposcillatoren: CMOS, TTL, afgeknotte sinusgolf, sinus, LVPECL, LVDS en HCSL.

Voor elk type worden de historische ontwikkeling, de elektrische eigenschappen, de typische signaalvorm en de voorkeurstoepassingsgebieden toegelicht.

2. Historische ontwikkeling

De ontwikkeling van de typen uitgangssignalen is nauw verbonden met de evolutie van halfgeleidertechnologie en de toenemende eisen aan klokfrequenties en signaalintegriteit:

2.1 TTL (Transistor-Transistor-Logica) – vanaf ca. 1964

TTL was een van de eerste breed verspreide digitale logicastandaarden en werd door Texas Instruments geïntroduceerd als de 7400-serie. Oscillatoren met TTL-uitgang werken met een voedingsspanning van 5 V en leveren niveaubereiken die direct compatibel zijn met TTL-poorten. De standaard heeft de digitale elektronica decennialang gevormd en was tot in de jaren ’90 de dominante logicastandaard.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – vanaf ca. 1968

CMOS-technologie werd oorspronkelijk ontwikkeld door RCA en kenmerkt zich door een extreem laag ruststroomverbruik. CMOS-oscillatoren leveren rail-to-rail uitgangssignalen, wat betekent dat de uitgang vrijwel volledig oscilleert tussen 0V en VCC. Door de voortdurende miniaturisatie en de trend naar lagere voedingsspanningen (3,3V, 2,5V, 1,8V) is CMOS de meest gebruikte uitgangsstandaard geworden voor kwadratuuroscillatoren.

2.3 Sinus – sinds het begin van de oscillatortechniek

Sinusvormige uitgangssignalen zijn zo oud als de oscillatortechnologie zelf. Kwadrantoscillatoren oscilleren fysiek sinusvormig; alle andere signaalvormen worden gegenereerd door de daaropvolgende schakelingen. Sinusvormige uitgangen hebben de voorkeur in hoogfrequente technologie, meetinstrumenten en analoge signaalverwerking omdat ze geen harmonischen genereren.

2.4 Clipped Sine Wave – vanaf ca. jaren ’70

De Clipped Sine Wave-uitgang vormt een compromis tussen sinus- en blokgolfuitgang. Het sinussignaal wordt aan de pieken begrensd (geclipt), waardoor steilere flanken ontstaan dan bij de zuivere sinus, maar minder harmonischen dan bij een blokgolfsignaal. Dit uitgangstype werd vooral gebruikt in de telecommunicatie en bij oudere hoogfrequenttoepassingen. Clipped Sine Wave-IC's worden tegenwoordig voornamelijk nog in TCXO's gebruikt. Met deze technologie kunnen aanzienlijk energiezuinigere TCXO's worden gebouwd dan met CMOS-technologie. CSW-TCXO's worden daarom als referentie gebruikt in navigatieapparatuur, noodoproepsystemen en gateways. Overal waar signaalbereik (radio) en zeer nauwkeurige positionering nodig zijn.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – vanaf ca. jaren ’90

Met de behoefte aan steeds hogere klokfrequenties in netwerk- en telecommunicatiesystemen ontstond LVPECL als snelle differentiële uitgangslogica. LVPECL is gebaseerd op de klassieke ECL-techniek (Emitter-Coupled Logic), die reeds in de jaren ’60 werd ontwikkeld voor hogesnelheidstoepassingen, en past deze aan voor lagere voedingsspanningen (3,3 V in plaats van -5,2 V). LVPECL biedt extreem korte schakeltijden en is geschikt voor frequenties ruim boven 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – vanaf 1994

LVDS werd in 1994 geïntroduceerd als ANSI/TIA/EIA-644-standaard en optimaliseert de differentiële signaaloverdracht voor laag stroomverbruik en hoge datasnelheden. De geringe differentiële spanningshub van slechts 350 mV maakt snelle schakelingen mogelijk met minimale elektromagnetische straling. LVDS is tegenwoordig wijdverbreid in display-interfaces, seriële dataverbindingen en FPGA-clocking.

2.7 HCSL (High-Speed Current Steering Logic) – vanaf ca. 2002

HCSL werd speciaal ontwikkeld voor de PCI Express-standaard en is sinds de eerste PCIe-generatie de referentieklokstandaard. De PCI-SIG specificeerde HCSL als een stroomgebaseerd differentieel signaal met zeer lage spanningshub, geoptimaliseerd voor de 100 MHz-referentieklokken in PCIe-systemen. HCSL is tegenwoordig onmisbaar in elke PC, server en embedded systeem met PCIe-interface.

3. Overzicht van signaalvormen

De volgende diagrammen tonen de geïdealiseerde signaalvormen van de zeven uitgangstypen. Let op de verschillende spanningsbereiken en signaalzwaaiäbs – diese sind entscheidend füä – deze zijn bepalend voor de compatibiliteit met de daaropvolgende ontvangers.ä

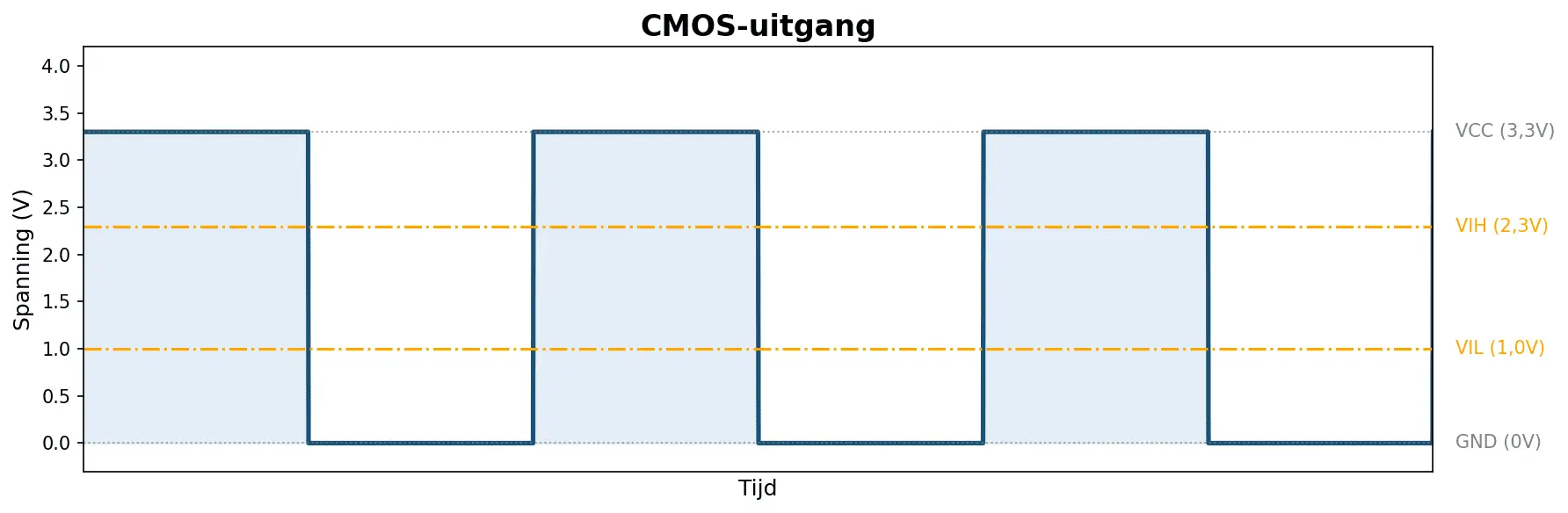

3.1 CMOS

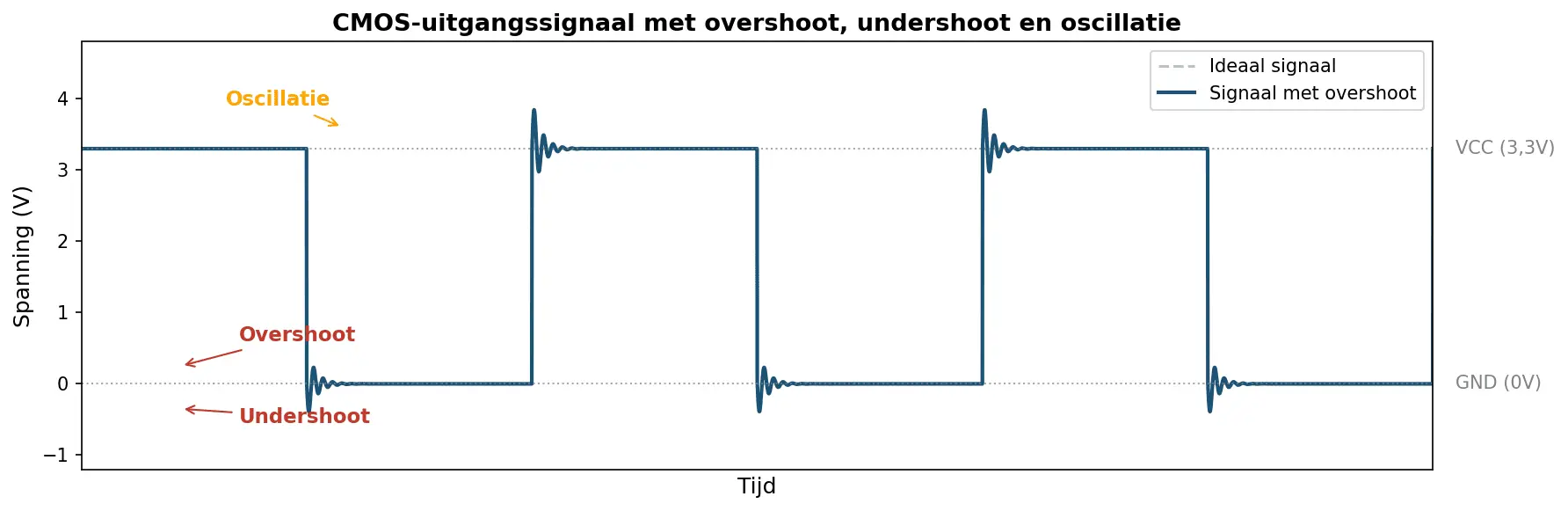

Afb. 1: CMOS-uitgangssignaal – Rail-to-rail-blokgolf tussen 0 V en VCC (hier 3,3 V)

Het CMOS-signaal kenmerkt zich door zijn volledige spanningshub tussen GND en VCC. De ingangsdrempels VIL en VIH liggen typisch bij 30 % respectievelijk 70 % van VCC, wat een ruime ruismarge garandeert. De symmetrische uitgangsdriverstructuren (P-kanaal/N-kanaal-MOSFET) maken vrijwel gelijke stijg- en daaltijden mogelijk.

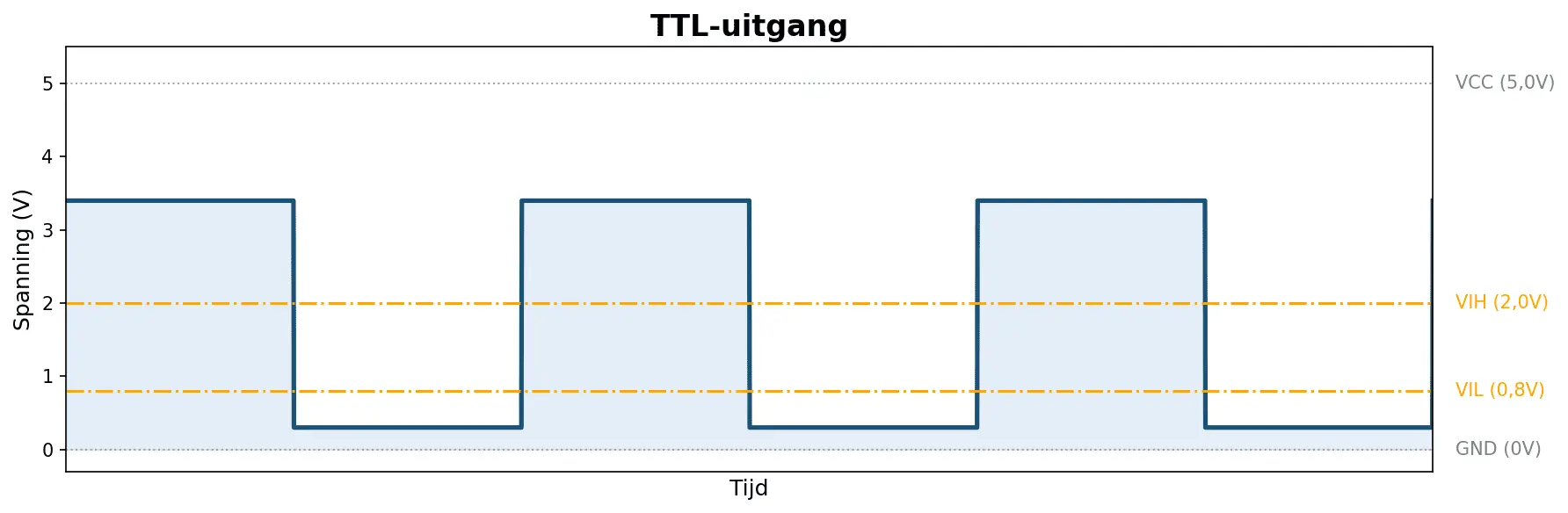

3.2 TTL

Afb. 2: TTL-uitgangssignaal – VOH typisch 3,4 V, VOL typisch 0,3 V bij 5 V voeding

In tegenstelling tot de CMOS-uitgang bereikt TTL geen rail-to-rail-niveaus. Het hoge niveau (VOH) ligt typisch bij 3,4 V (minimaal 2,4 V), het lage niveau (VOL) bij maximaal 0,4 V. De asymmetrische drempels (VIL = 0,8 V, VIH = 2,0 V) zijn het gevolg van de bipolaire transistorarchitectuur. Het zogenaamde „verboden gebied“ tussen 0,8 V en 2,0 V mag in statisch bedrijf niet worden aangenomen.

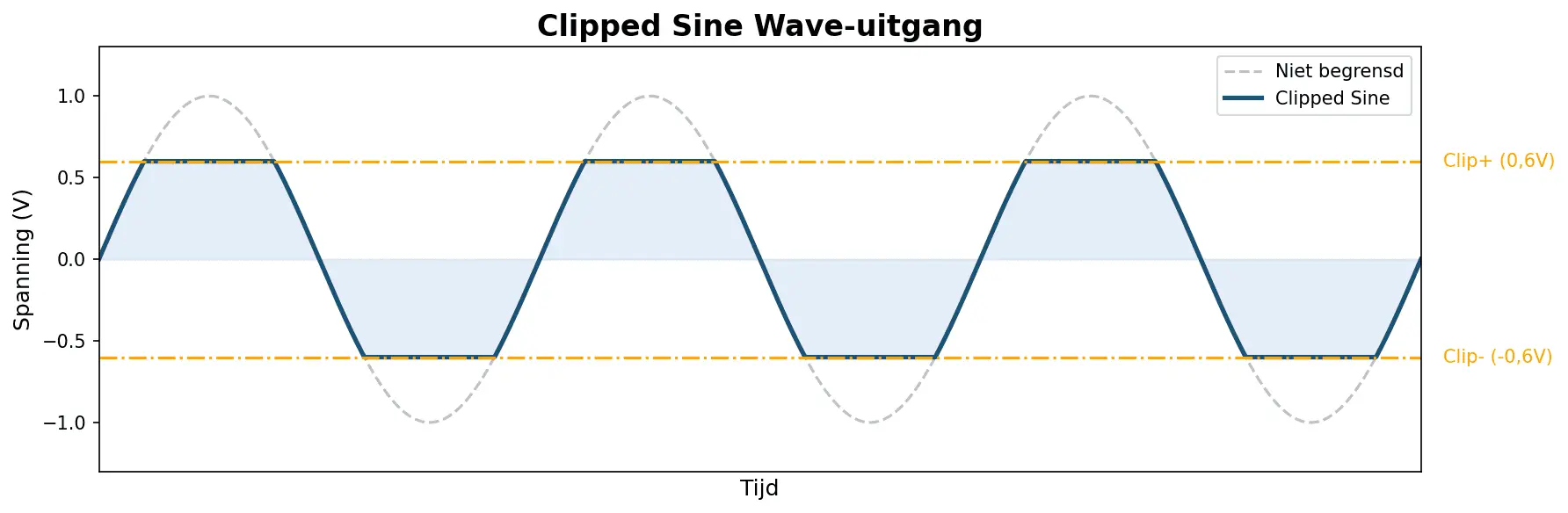

3.3 Clipped Sine Wave

Afb. 3: Clipped Sine Wave-uitgang – Sinussignaal met beperkte amplitudepieken

Bij de Clipped Sine Wave-uitgang wordt het natuurlijke sinussignaal van de kwartsresonator op gedefinieerde drempelwaarden begrensd. De stippellijn toont het onbeperkte sinusverloop. Door de clipping ontstaan steilere nuldoorgangen dan bij de zuivere sinus, wat de aansturing van de daaropvolgende logica vergemakkelijkt, terwijl het harmonischengehalte gematigd blijft.

3.4 Sinus

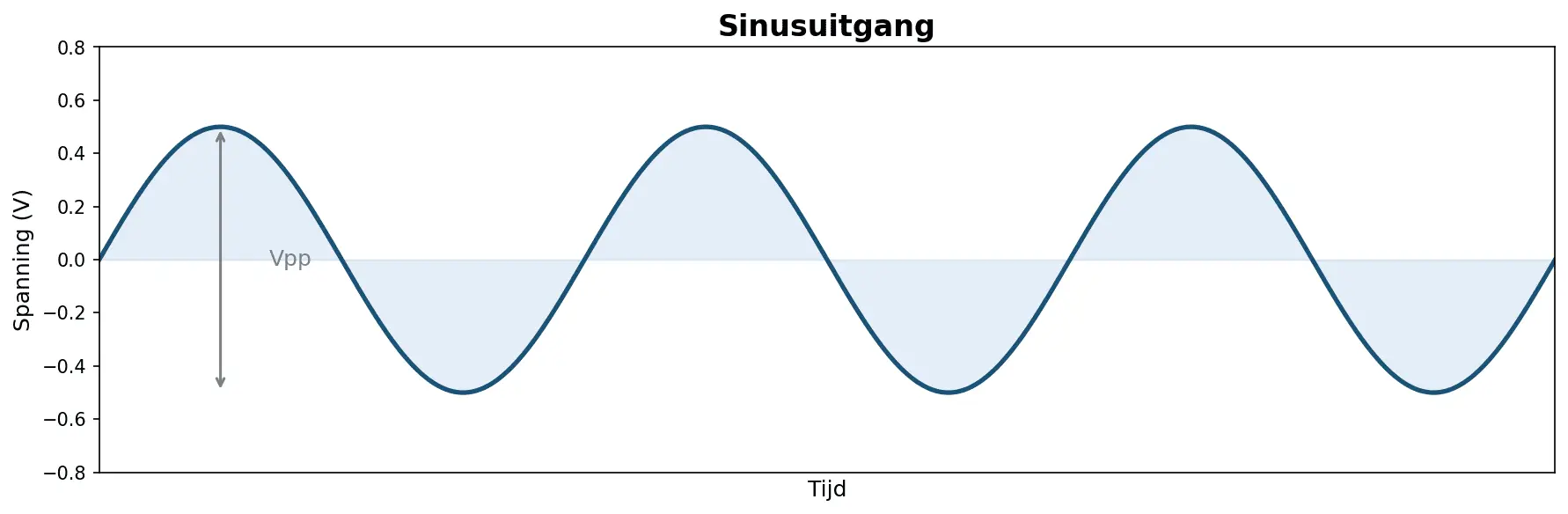

Afb. 4: Sinus-uitgang – Zuiver sinussignaal met gedefinieerde piek-piekspanning (Vpp)

De sinusuitgang levert het zuiverste spectrum van alle uitgangsvormen: idealiter slechts één enkele spectraallijn bij de grondfrequentie. De amplitude wordt aangegeven als piek-piekspanning (Vpp) of als vermogen in dBm. Typische waarden liggen bij 0,5 tot 1,0 Vpp of 0 tot +13 dBm in 50 Ω-systemen.

3.5 LVPECL

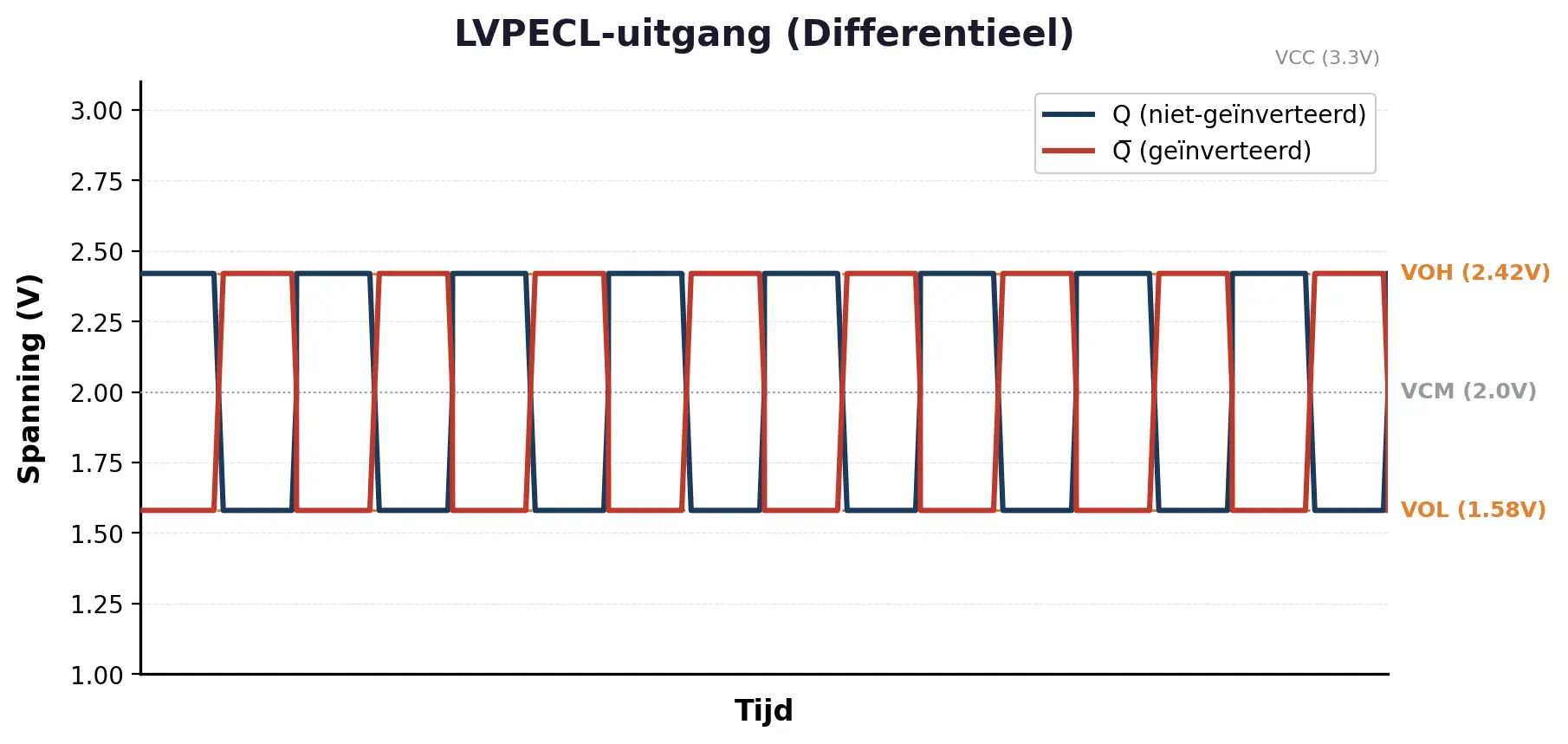

Afb. 5: LVPECL-uitgang – Differentieel signaal met ca. 800 mV totale hub rond VCC–1,3 V

LVPECL maakt gebruik van differentiële signaalvoering: twee complementaire uitgangen (Q en Q̅) schakelen in tegenfase rond een gemeenschappelijk gleichtaktniveau (VCM), dat typisch bij VCC–1,3 V ligt. De differentiële spanningshub bedraagt ca. 800 mV. De stroombronarchitectuur maakt extreem snelle schakeltijden mogelijk met minimale neiging tot overshoot.

3.6 LVDS

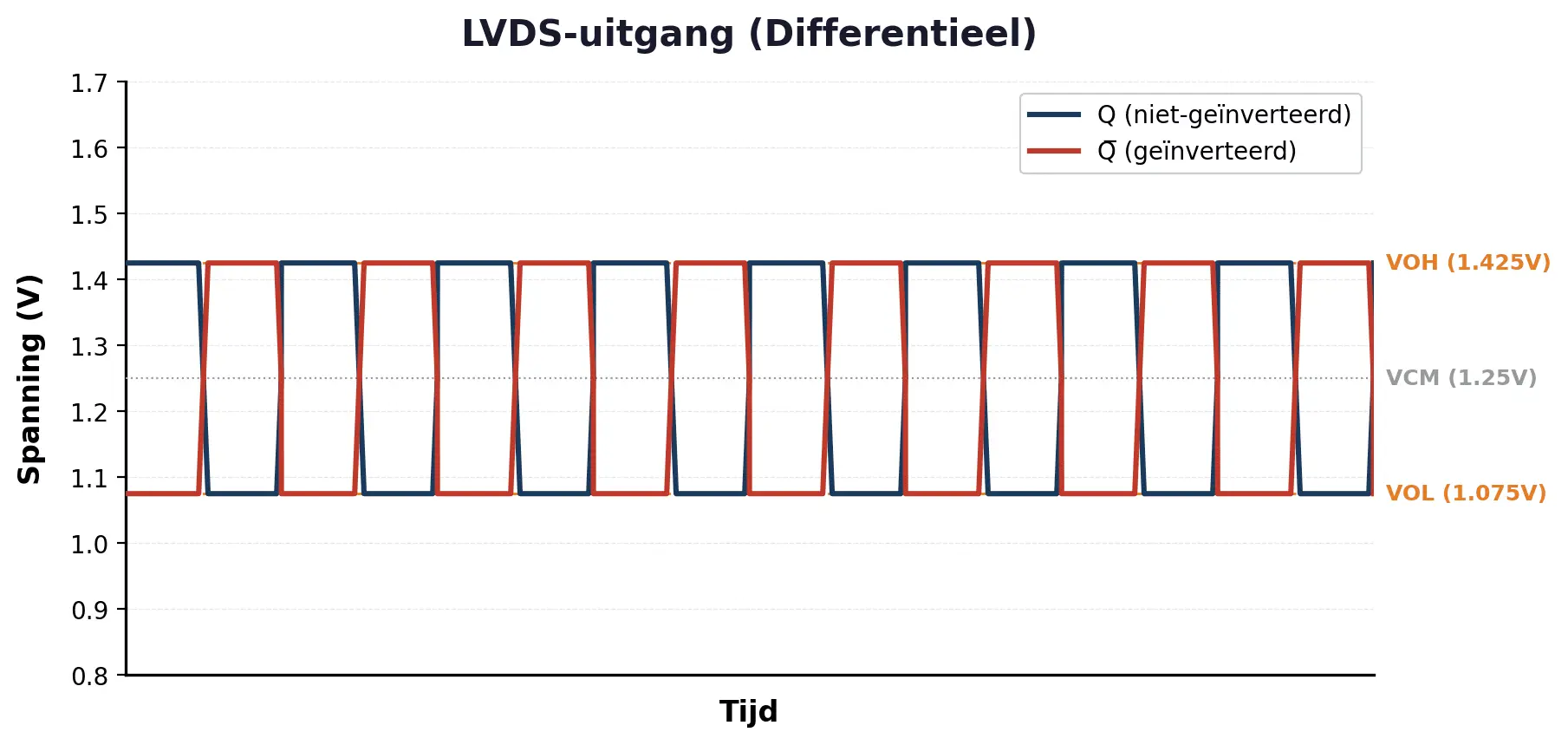

Afb. 6: LVDS-uitgang – Differentieel signaal met slechts 350 mV hub rond 1,25 V gleichtaktniveau

LVDS kenmerkt zich door zijn bijzonder lage differentiële spanningshub van slechts 350 mV. Het gleichtaktniveau ligt bij 1,25 V. Door de stroomgestuurde driver (typisch 3,5 mA) en de 100 Ω-terminatie wordt een hoge signaalintegriteit bereikt bij minimaal stroomverbruik. De lage amplitude minimaliseert elektromagnetische straling.

3.7 HCSL

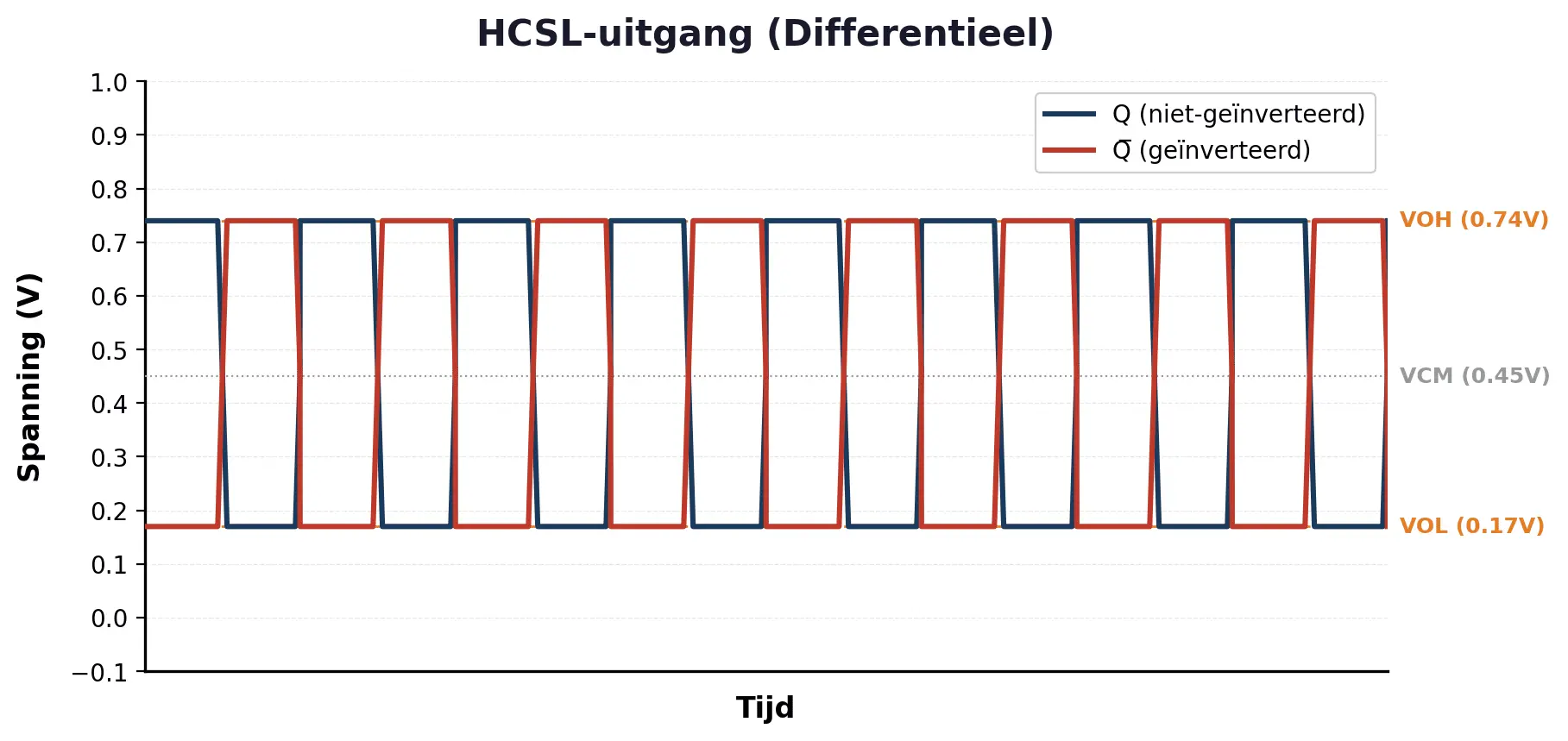

Afb. 7: HCSL-uitgang – Stroomgebaseerd differentieel signaal voor PCIe-referentieklokken

HCSL werkt met een zeer lage spanningshub: VOH ligt typisch bij 0,74 V en VOL bij 0,17 V, resulterend in een gleichtaktniveau van ca. 0,45 V. De stroomstuurarchitectuur is specifiek geoptimaliseerd voor de eisen van de PCIe-specificatie en maakt een nauwkeurige impedantieaanpassing mogelijk via 50 Ω-terminaties naar massa.

4. Vergelijking van de uitgangssignalen

De volgende tabel vat de belangrijkste eigenschappen van alle zeven uitgangstypen samen:

Typ | Soort signaal | VCC (V) | VOH/ VOL (V) | Verschil Slag | Max. gesch. freq. | Typische toepassing |

| CMOS | Single- Ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Microcontrollers, FPGA's, algemene digitale techniek |

| TTL | Single- Ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Legacy-systemen, industriële besturingen |

| Clipped Sine | Single- Ended | 1,8/2,5/3,3 | variabel | - | ~200 MHz | Telecommunicatie, HF-toepassingen |

| Sinus | Single- Ended | 3,3/5,0/12 | variabel | - | >1 GHz | HF-techniek, meetapparatuur, frequentiesynthese |

| LVPECL | Differentieel | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Netwerkapparatuur, SONET/SDH, hogesnelheidsklokken |

| LVDS | Differentieel | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Display-interfaces, seriële verbindingen, FPGA-clocking |

| HCSL | Differentieel | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | PCI Express-referentieklok (100 MHz) |

5. Belangrijke verschillen in detail

5.1 Single-Ended vs. Differentieel

Het meest fundamentele verschil tussen de uitgangstypen is de signaalvoering. CMOS, TTL, Clipped Sine Wave en Sinus zijn single-ended signalen – ze refereren aan een gemeenschappelijke massa. LVPECL, LVDS en HCSL daarentegen zijn differentiële signalen met twee complementaire lijnen. Differentiële signalen bieden beslissende voordelen bij hogere frequenties: ze onderdrukken gleichtaktstoringen, maken kleinere spanningshubben mogelijk en zorgen daardoor voor snellere schakeltijden bij minder elektromagnetische straling.

5.2 Spanningshub en ruismarge

CMOS biedt met zijn rail-to-rail-uitgang de grootste absolute spanningshub en daarmee de beste statische ruismarge. TTL heeft door de asymmetrische niveaus een beperktere ruismarge. De differentiële standaarden (LVPECL, LVDS, HCSL) compenseren hun kleinere spanningshubben door de gleichtaktonderdrukking van de differentiële transmissie, waardoor ze in gestoorde omgevingen vaak betrouwbaarder werken dan single-ended signalen.

5.3 Stroomverbruik

CMOS-oscillatoren verbruiken in statische toestand vrijwel geen stroom; het verbruik stijgt proportioneel met de frequentie (dynamisch vermogensverlies). TTL heeft een constant hoger ruststoomverbruik vanwege de bipolaire architectuur. LVPECL vereist externe afsluitweerstanden en heeft het hoogste stroomverbruik van de differentiële standaarden. LVDS staat bekend om zijn lage stroomverbruik (typisch 3,5 mA driverstroom). HCSL zit qua stroomverbruik tussen LVDS en LVPECL.

5.4 Frequentiebereik en toepassingszwaartepunten

Voor frequenties tot ongeveer 200 MHz zijn CMOS-oscillatoren in de meeste gevallen de eerste keuze vanwege hun veelzijdigheid, eenvoudige circuitontwerp en brede beschikbaarheid. Boven ongeveer 200 MHz worden differentiële uitgangen aanbevolen. LVPECL biedt de hoogste frequenties (>3 GHz) en wordt gebruikt in netwerk- en telecommunicatieapparatuur. LVDS bestrijkt een breed middenbereik en is met name gangbaar in FPGA- en displaytoepassingen. HCSL is geoptimaliseerd voor zijn specifieke gebruikssituatie: de 100 MHz referentieklok voor PCI Express.

5.5 Terminatie en schakelingscomplexiteit

CMOS- en TTL-uitgangen vereisen doorgaans geen externe terminatie bij korte geleiderlengtes – dit maakt ze bijzonder eenvoudig in gebruik. LVPECL vereist verplicht externe afsluitweerstanden (typisch: Thévenin-terminatie naar VCC–2 V of weerstanden naar massa), wat de schakelingscomplexiteit verhoogt. LVDS wordt standaard getermineerd met een 100 Ω-differentiaalweerstand bij de ontvanger. HCSL gebruikt 50 Ω-weerstanden naar massa bij elke uitgang.

6. Overshoot bij oscillator-uitgangssignalen

6.1 Wat is overshoot?

Overshoot en undershoot zijn korte spanningspieken die optreden tijdens snelle schakelhandelingen. Bij een stijgende flank overschrijdt de spanning kortstondig VCC (overshoot), terwijl deze bij een dalende flank iets onder GND zakt (undershoot). Deze pieken worden vaak gevolgd door gedempte oscillaties die bekend staan als "ringing".

De oorzaak ligt in de combinatie van de zeer steile schakelflank van de uitgangsdriver en de parasitaire inducties en capaciteiten van de geleiderbaan, de behuizing en de lastcapaciteit. Fysisch gezien ontstaat een resonantiekring uit de leidingsinductie en de ingangscapaciteit van de ontvanger. Hoe steiler de schakelflank en hoe langer de geleiderbaan, des te sterker de overshoot.

Afb. 8: CMOS-uitgangssignaal met overshoot – Overshoot boven VCC, undershoot onder GND en daaropvolgende ringing

6.2 Waarom is overshoot problematisch?

Overshoots die boven VCC of onder GND komen, kunnen de ESD-beveiligingsdiodes van de ontvanger-IC in de voorwaartse richting polariseren, waardoor parasitaire stromen ontstaan. In het ergste geval kan dit leiden tot latch-up – een ongecontroleerde stroom door parasitaire thyristorstructuren in de CMOS-IC, wat het component kan beschadigen. Ernstige rimpelingen kunnen ook leiden tot meervoudige triggering bij klokingangen als de spanning meerdere keren de schakeldrempel overschrijdt, met als gevolg foutief systeemgedrag.

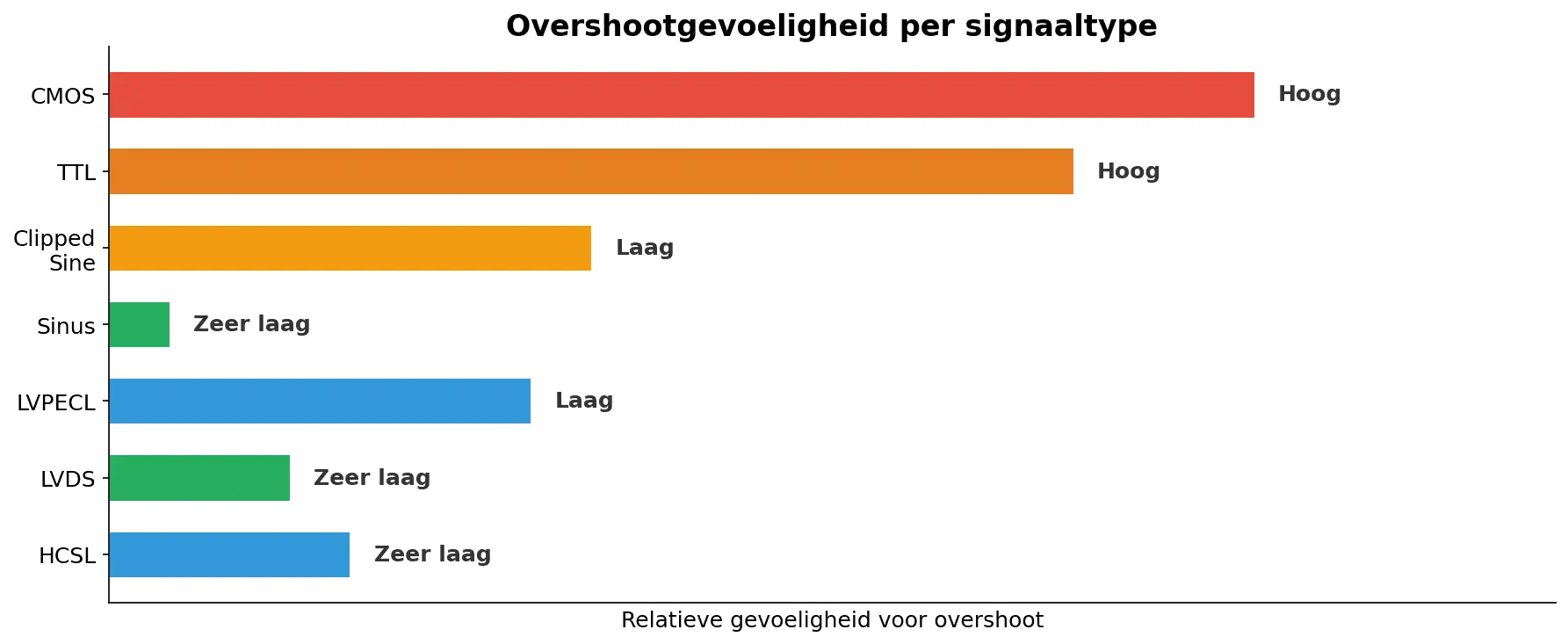

6.3 Vergelijking: overshoot per signaaltype

De gevoeligheid voor overshoot verschilt aanzienlijk tussen de verschillende uitgangstypen. De volgende grafiek toont de relatieve gevoeligheid in vergelijking:

6.4 Overshoot bij single-ended signalen

CMOS: Het sterkst getroffen. De symmetrische P-/N-kanaal-MOSFET-drivers genereren zeer steile flanken die in combinatie met leidingsinducties uitgesproken overshoot veroorzaken. Vooral bij moderne laagspannings-CMOS-oscillatoren (1,8 V) kan de overshoot relatief ten opzichte van de voedingsspanning significant zijn.

TTL: Eveneens gevoelig, zij het om iets andere redenen. De asymmetrische totem-pole-uitgangstrap genereert bij de stijgende flank een korte stroompiek wanneer beide transistoren gelijktijdig geleiden (cross-conduction). De typisch iets tragere flanken ten opzichte van modern CMOS verzachten het probleem enigszins.

Clipped Sine Wave: Aanzienlijk minder gevoelig. Door de beperkte amplitudepieken en de relatief zachte flanken ontstaat aanzienlijk minder hoogfrequente energie die reflecties en ringing zou kunnen aanwakkeren. De clipping werkt als een natuurlijke amplitudebeperking die overshoot al in het signaal onderdrukt.

Sinusgolf: Vrijwel immuun voor klassieke overshoot. Omdat het signaal geen abrupte overgangen bevat, wordt er geen breedbandige energiepuls gegenereerd die lijnresonanties zou kunnen opwekken. Impedantie-mismatch kan echter leiden tot staande golven en reflecties die de signaalamplitude op bepaalde punten veranderen. Dit wordt geregeld door klassieke RF-terminatie (50Ω of 75Ω terminatie).

6.5 Overshoot bij differentiële signalen

LVPECL: Dankzij de stroombron-uitgangstrap inherent goed onderdrukt. De stroomsturing begrenst de maximale flanksteilheid op natuurlijke wijze. Bij onvoldoende terminatie kunnen toch reflecties optreden, aangezien LVPECL op zeer hoge frequenties werkt. De juiste Thévenin- of emittervolger-schakeling is hier doorslaggevend – niet primair vanwege overshoot, maar om het juiste werkpunt te garanderen en reflecties te vermijden.

LVDS: Zeer robuust door ontwerp. De stroomgestuurde driver levert een constante stroom van typisch 3,5 mA in de 100 Ω-differentiaalterminatie, waardoor de spanningshub fysisch begrensd wordt. Zelfs bij impedantiediscontinuiteiten blijven reflecties klein, aangezien de geringe spanningshub van slechts 350 mV weinig energie voor storingen levert. LVDS is een van de meest vergevingsgezinde standaarden wat betreft signaalintegriteit.

HCSL: Gedraagt zich vergelijkbaar met LVDS dankzij de stroomgebaseerde architectuur. De zeer lage spanningshub en de 50 Ω-terminatie naar massa zorgen voor een schone impedantieaanpassing. In de PCIe-specificatie zijn de toelaatbare overshoots expliciet gedefinieerd en strak getoleranteerd, zodat HCSL-conforme oscillatoren inherent aan deze eisen voldoen.

6.6 Tegenmaatregelen voor de beheersing van overshoot

De meest effectieve maatregel bij single-ended signalen (met name CMOS en TTL) is een serieweerstand direct aan de uitgang van de oscillator, typisch in het bereik van 22 tot 47 Ω. Deze weerstand vormt samen met de leidingsimpedantie een spanningsdeler die de flank dempt en reflecties absorbeert. De optimale waarde resulteert uit het verschil tussen leidingsimpedantie en uitgangsimpedantie van de driver.

Daarnaast helpen korte, impedantiegecontroleerde geleiderbanen, minimalisatie van doorverbindingen (via's) op de kloklijn, een doorlopend massavlak onder de signaallijn en voldoende ontkoppelcondensatoren nabij de oscillator (typisch 100 nF keramisch plus 10 µF). Sommige CMOS-oscillatorfabrikanten bieden bovendien modellen met gecontroleerde flanksteilheid (Slew Rate Control) aan, die het probleem al in de driver verminderen.

Bij differentiële signalen (LVPECL, LVDS, HCSL) is de juiste, specificatieconforme terminatie de belangrijkste maatregel. Daarnaast moeten de twee lijnen van een differentieel paar altijd met gelijke lengte en nauwe koppeling worden geleid om skew (looptijdverschillen) te minimaliseren en de gleichtaktonderdrukking te behouden.

7. Keuzehulp

De keuze van het juiste uitgangstype hangt in wezen af van vier factoren: de vereiste klokfrequentie, de logicafamilie van de ontvanger, het beschikbare vermogensbudget en de eisen aan de signaalintegriteit.

Toepassing | Aanbeveling |

| Algemene digitale techniek, µC, FPGA-I/O (tot ~200 MHz) | CMOS – Eenvoudigste en voordeligste oplossing, rail-to-rail, breedste beschikbaarheid, flexibel in voedingsspanning (1,8–5,0 V) |

| Legacy 5V-systemen, industriële besturingen | TTL – Direct compatibel met oudere 5V-logicafamilies; wordt steeds meer vervangen door CMOS met 5V-voeding |

| HF-toepassingen, transformator- gebaseerde schakelingen | Clipped Sine Wave of Sinus – Lager harmonischengehalte vermindert EMC-problemen en maakt nauwkeurige frequentiesynthese mogelijk |

Hogesnelheidsnetwerkapparatuur (>622 MHz) | LVPECL – Hoogste schakelsnelheid, ideaal voor SONET/SDH, Ethernet-PHY's en backplane-klokken |

| FPGA-clocking, seriële data- overdracht, display-interfaces | LVDS – Optimaal compromis tussen snelheid, stroomverbruik en EMC-gedrag |

| PCI Express-referentieklok | HCSL – Enige door de PCI-SIG gespecificeerde klokstandaard voor PCIe-systemen |