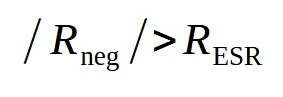

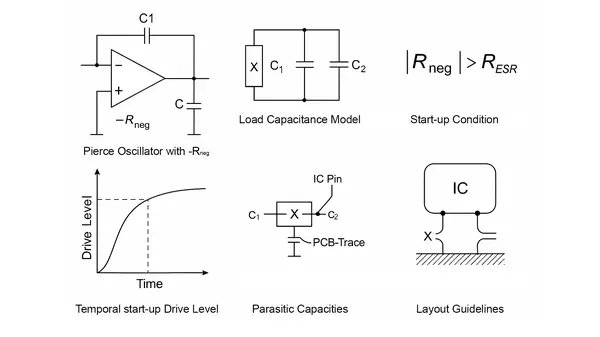

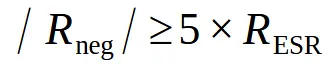

Dit betekent dat de waarde van de negatieve ingangsweerstand groter moet zijn dan de serieweerstand (ESR) van het kristal.

Alleen dan is er een nettoversterking die tot oscillatie leidt.

F.2: Invloed op de transiëntresponsveiligheid

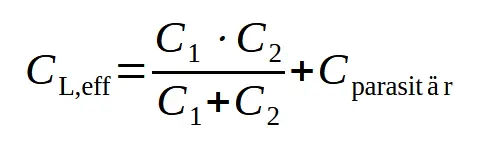

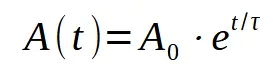

Als de waarde van de negatieve ingangsweerstand te klein is (d.w.z. -Rneg is te zwak), gebeurt het volgende:

- Het kristal ontvangt te weinig energie → langzame oscillatie of helemaal geen oscillatie

- Oscillatie start pas bij een hogere voedingsspanning of temperatuur

- Opstarten in bedrijfsmodi met laag vermogen wordt onbetrouwbaar

Typische oorzaak:

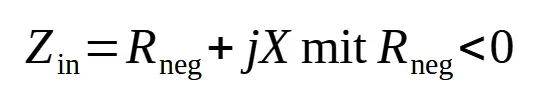

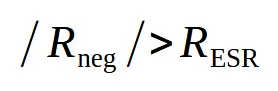

Sommige moderne MCU's hebben zwakke oscillatorversterkers om efficiëntieredenen, wat betekent dat -Rneg kleiner is dan in oudere IC-generaties. Tegelijkertijd werken veel ontwerpen met kleine belastingscapaciteiten of lange sporen, waardoor de parasitaire verliezen toenemen.

V.3: Waarom zijn kristallen met een lage ESR bijzonder belangrijk?

De ESR van het kristal bepaalt de interne verliezen. Een lage ESR betekent

- lagere verliezen

- lagere noodzakelijke tegenversterking

- hoge transiëntstabiliteit, zelfs met zwakke oscillatortrappen

- kortere opstarttijd

- stabielere oscillatie over temperatuur

Praktische aanbevelingen:

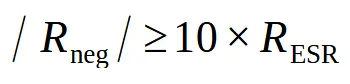

- Gebruik kristallen waarvan de ESR aanzienlijk lager is dan de maximumwaarde die door het IC wordt gespecificeerd.

- Als een microcontroller bijvoorbeeld een maximale ESR van 70 Ω specificeert, is een kristal met een ESR van 30-50 Ω ideaal. Dit laat voldoende veiligheidsmarge tegen een mogelijk lage negatieve ingangsweerstand van de oscillator.

F.4: Conclusie over de interactie van -Rneg en kwarts ESR

De betrouwbaarheid van de transiëntrespons hangt in essentie af van het volgende:

- de interne oscillator biedt voldoende negatieve ingangsweerstand,

- het kristal heeft een voldoende lage ESR,

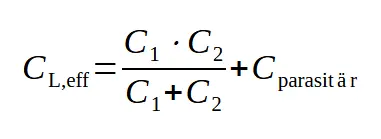

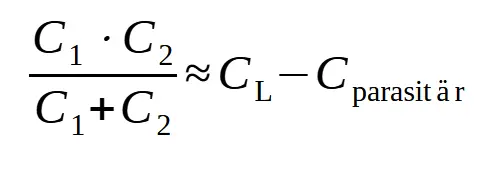

- de belastingscapaciteiten zijn correct gedimensioneerd.

Alleen als de verhouding tussen -Rneg en ESR correct is, zal het kristal snel en betrouwbaar starten over het hele temperatuur- en spanningsbereik.